# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

## QUADRUPLE BILATERAL SWITCHES

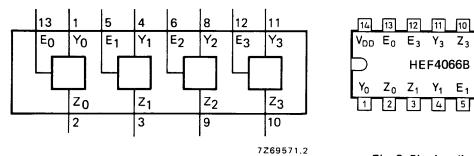

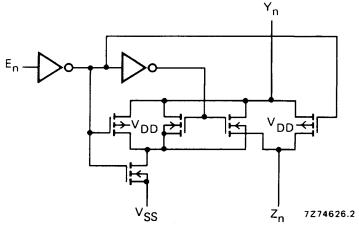

The HEF4066B has four independent bilateral analogue switches (transmission gates). Each switch has two input/output terminals (Y/Z) and an active HIGH enable input (E). When E is connected to  $V_{DD}$  a low impedance bidirectional path between Y and Z is established (ON condition). When E is connected to  $V_{SS}$  the switch is disabled and a high impedance between Y and Z is established (OFF condition).

The HEF4066B is pin compatible with the HEF4016B but exhibits a much lower ON resistance. In addition the ON resistance is relatively constant over the full input signal range.

Fig. 2 Pinning diagram.

7769712

Fig. 1 Functional diagram.

#### PINNING

$E_0$  to  $E_3$  enable inputs  $Y_0$  to  $Y_3$  input/output terminals  $Z_0$  to  $Z_3$  input/output terminals HEF4066BP(N): 14-lead DIL; plastic (SOT27-1) HEF4066BD(F): 14-lead DIL; ceramic (cerdip) (SOT73)) HEF4066BT(D): 14-lead SO; plastic (SOT108-1) (): Package Designator North America

#### **APPLICATION INFORMATION**

An example of application for the HEF4066B is:

Analogue and digital switching

Fig. 3 Schematic diagram (one switch).

### RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134) Power dissipation per switch

For other RATINGS see Family Specifications

### D.C. CHARACTERISTICS

$T_{amb} = 25 \text{ °C}$

-

|                                                  | V <sub>DD</sub><br>V | symbol           | min.            | typ.                 | max.               |                | conditions                                                                                                    |

|--------------------------------------------------|----------------------|------------------|-----------------|----------------------|--------------------|----------------|---------------------------------------------------------------------------------------------------------------|

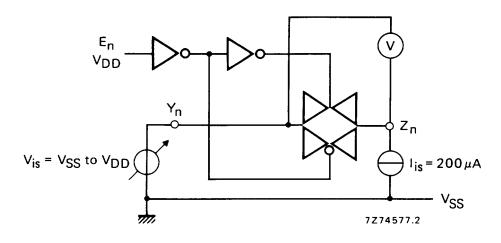

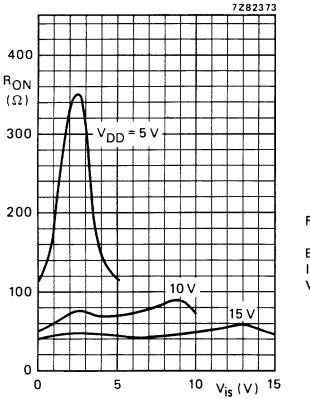

| ON resistance                                    | 5<br>10<br>15        | R <sub>ON</sub>  |                 | 350<br>80<br>60      | 2500<br>245<br>175 | Ω<br>Ω<br>Ω    | $\begin{cases} E_n \text{ at } V_{DD} \\ V_{is} = V_{SS} \text{ to } V_{DD} \\ \text{see Fig. 4} \end{cases}$ |

| ON resistance                                    | 5<br>10<br>15        | R <sub>ON</sub>  | -<br>  -<br>  - | 115<br>50<br>40      | 340<br>160<br>115  | Ω<br>Ω<br>Ω    | E <sub>n</sub> at V <sub>DD</sub><br>V <sub>is</sub> = V <sub>SS</sub><br>see Fig. 4                          |

| ON resistance                                    | 5<br>10<br>15        | R <sub>ON</sub>  | -<br>-<br>-     | 120<br>65<br>50      | 365<br>200<br>155  | Ω<br>Ω<br>Ω    | E <sub>n</sub> at V <sub>DD</sub><br>V <sub>is</sub> = V <sub>DD</sub><br>see Fig. 4                          |

| 'Δ' ON resistance<br>between any two<br>channels | 5<br>10<br>15        | ΔR <sub>ON</sub> | _<br>_<br>_     | 25<br>10<br>5        | -                  | Ω<br>Ω<br>Ω    | E <sub>n</sub> at V <sub>DD</sub><br>V <sub>is</sub> = V <sub>SS</sub> to V <sub>DD</sub><br>see Fig. 4       |

| OFF state leakage<br>current, any<br>channel OFF | 5<br>10<br>15        | loz              | -<br>  -<br>  - | <br><br>_            | <br><br>200        | nA<br>nA<br>nA | E <sub>n</sub> at V <sub>SS</sub>                                                                             |

| E <sub>n</sub> input voltage<br>LOW              | 5<br>10<br>15        | VIL              | -<br>  -<br>  - | 2,25<br>4,50<br>6,75 | 1<br>2<br>2        | V<br>V<br>V    | $\begin{cases} I_{is} = 10 \ \mu A \\ see Fig. 9 \end{cases}$                                                 |

|                                            | V <sub>DD</sub><br>V | symbol | T<br>-40<br>max.  | amb ( <sup>0</sup> (<br>+ 25<br>max. | C)<br>+ 85<br>max.  |                | conditions                                                                                           |

|--------------------------------------------|----------------------|--------|-------------------|--------------------------------------|---------------------|----------------|------------------------------------------------------------------------------------------------------|

| Quiescent device<br>current                | 5<br>10<br>15        | IDD    | 1,0<br>2,0<br>4,0 | 1,0<br>2,0<br>4,0                    | 7,5<br>15,0<br>30,0 | μΑ<br>μΑ<br>μΑ | $\begin{cases} V_{SS} = 0; all valid \\ input combinations; \\ V_{I} = V_{SS} or V_{DD} \end{cases}$ |

| Input leakage<br>current at E <sub>n</sub> | 15                   | ±IN    | _                 | 300                                  | 1000                | nA             | E <sub>n</sub> at V <sub>SS</sub> or V <sub>DD</sub>                                                 |

Product specification

HEF4066B

gates

P max. 100 mW

HEF4066B gates

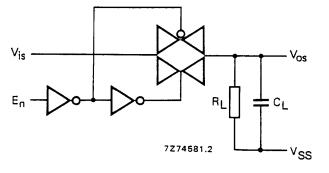

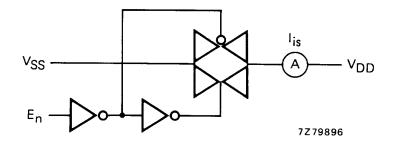

Fig. 4 Test set-up for measuring RON.

Fig. 5 Typical  $R_{\mbox{ON}}$  as a function of input voltage.

$E_n \text{ at } V_{DD}$  $I_{is} = 200 \ \mu\text{A}$  $V_{SS} = 0 \ V$

### NOTE

To avoid drawing V<sub>DD</sub> current out of terminal Z, when switch current flows into terminals Y, the voltage drop across the bidirectional switch must not exceed 0,4 V. If the switch current flows into terminal Z, no V<sub>DD</sub> current will flow out of terminals Y, in this case there is no limit for the voltage drop across the switch, but the voltages at Y and Z may not exceed V<sub>DD</sub> or V<sub>SS</sub>.

## HEF4066B gates

#### A.C. CHARACTERISTICS

$V_{\mbox{\scriptsize SS}}$  = 0 V;  $T_{\mbox{\scriptsize amb}}$  = 25 °C; input transition times  $\leqslant$  20 ns

|                                                                                       | V <sub>DD</sub><br>V     | symbol                   | typ.                                                                    | max.                       |                                                                                                     |                                    |

|---------------------------------------------------------------------------------------|--------------------------|--------------------------|-------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------|

| Propagation delays<br>V <sub>is</sub> — V <sub>os</sub><br>HIGH to LOW<br>LOW to HIGH | 5<br>10<br>15<br>5<br>10 | <sup>t</sup> PHL<br>tPLH | 10<br>5<br>5<br>10<br>5                                                 | 20<br>10<br>10<br>20<br>10 | ns<br>ns<br>ns<br>ns<br>ns                                                                          | <pre>&gt; note 1 &gt; note 1</pre> |

|                                                                                       | 15                       |                          | 5                                                                       | 10                         | ns                                                                                                  | J                                  |

| Output disable times<br>E <sub>n</sub> → V <sub>os</sub><br>HIGH                      | 5<br>10<br>15            | <sup>t</sup> PHZ         | 80<br>65<br>60                                                          | 160<br>130<br>120          | ns<br>ns<br>ns                                                                                      | } note 2                           |

| LOW                                                                                   | 5<br>10<br>15            | <sup>t</sup> PLZ         | 80<br>70<br>70                                                          | 160<br>140<br>140          | ns<br>ns<br>ns                                                                                      | } note 2                           |

| Output enable times<br>E <sub>n</sub> ─► V <sub>OS</sub><br>HIGH                      | 5<br>10<br>15            | <sup>t</sup> PZH         | 40<br>20<br>15                                                          | 80<br>40<br>30             | ns<br>ns<br>ns                                                                                      | } note 2                           |

| LOW                                                                                   | 5<br>10<br>15            | <sup>t</sup> PZL         | 45<br>20<br>15                                                          | 90<br>40<br>30             | ns<br>ns<br>ns                                                                                      | } note 2                           |

| Distortion, sine-wave<br>response                                                     | 5<br>10<br>15            |                          | 0,25<br>0,04<br>0,04                                                    |                            | %<br>%<br>%                                                                                         | } note 3                           |

| Crosstalk between<br>any two channels                                                 | 5<br>10<br>15            |                          | -<br>1<br>-                                                             |                            | MHz<br>MHz<br>MHz                                                                                   | } note 4                           |

| Crosstalk; enable<br>input to output                                                  | 5<br>10<br>15            |                          | _<br>50<br>_                                                            |                            | mV<br>mV<br>mV                                                                                      | } note 5                           |

| OFF-state<br>feed-through                                                             | 5<br>10<br>15            |                          | _<br>  1<br>  _                                                         |                            | MHz<br>MHz<br>MHz                                                                                   | } note 6                           |

| ON-state frequency<br>response                                                        | 5<br>10<br>15            |                          | <br>90<br>                                                              |                            | MHz<br>MHz<br>MHz                                                                                   | } note 7                           |

|                                                                                       | V <sub>DD</sub><br>V     | typical fo               | rmula for                                                               | Ρ (μW)                     | where<br>f <sub>i</sub> = input freq. (MHz)<br>f <sub>o</sub> = output freq. (MHz)                  |                                    |

| Dynamic power<br>dissipation per<br>package (P)                                       | 5<br>10<br>15            | 3 500 f <sub>i</sub>     | + Σ(f <sub>o</sub> CL<br>+ Σ(f <sub>o</sub> CL<br>+ Σ(f <sub>o</sub> CL | $\times V_{DD}^{2}$        | $C_L$ = load capacitance (pF)<br>$\Sigma(f_0C_L)$ = sum of outputs<br>$V_{DD}$ = supply voltage (V) |                                    |

HEF4066B gates

#### NOTES

$V_{is}$  is the input voltage at a Y or Z terminal, whichever is assigned as input.  $V_{os}$  is the output voltage at a Y or Z terminal, whichever is assigned as output.

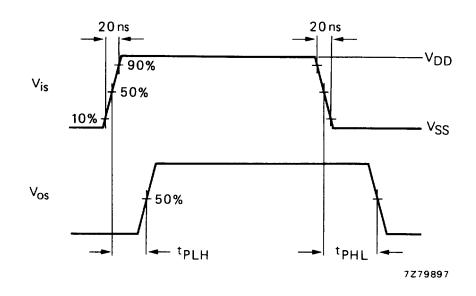

- 1.  $R_L = 10 \text{ k}\Omega$  to  $V_{SS}$ ;  $C_L = 50 \text{ pF}$  to  $V_{SS}$ ;  $E_n = V_{DD}$ ;  $V_{is} = V_{DD}$  (square-wave); see Figs 6 and 10.

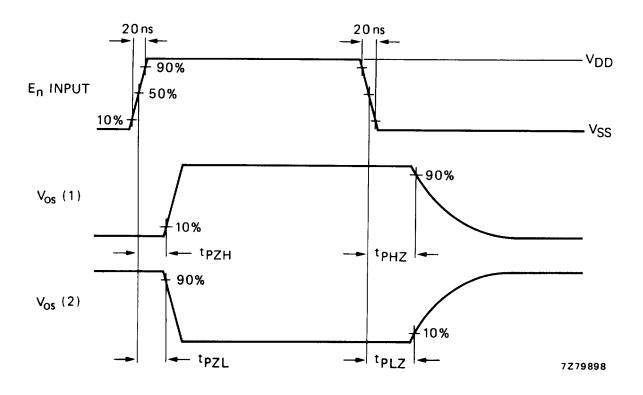

- 2.  $R_L = 10 k\Omega$ ;  $C_L = 50 pF$  to  $V_{SS}$ ;  $E_n = V_{DD}$  (square-wave);  $V_{is} = V_{DD}$  and  $R_L$  to  $V_{SS}$  for  $t_{PHZ}$  and  $t_{PZH}$ ;

- $V_{is} = V_{SS}$  and  $R_{L}$  to  $V_{DD}$  for tpLZ and tpZL; see Figs 6 and 11.

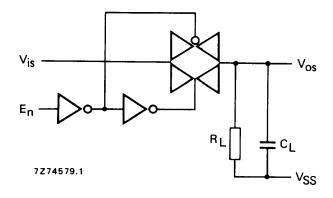

- 3.  $R_L = 10 k\Omega$ ;  $C_L = 15 pF$ ;  $E_n = V_{DD}$ ;  $V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );  $f_{is} = 1 kHz$ ; see Fig. 7.

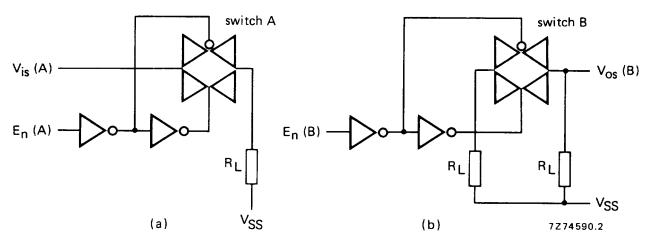

- 4.  $R_{L} = 1 k\Omega$ ;  $V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ ); 20 log  $\frac{V_{os}(B)}{V_{is}(A)} = -50 dB$ ;  $E_{n}(A) = V_{SS}$ ;  $E_{n}(B) = V_{DD}$ ; see Fig. 8.

- 5.  $R_L = 10 \text{ k}\Omega$  to  $V_{SS}$ ;  $C_L = 15 \text{ pF}$  to  $V_{SS}$ ;  $E_n = V_{DD}$  (square-wave); crosstalk is  $|V_{OS}|$  (peak value); see Fig. 6.

- 6.  $R_L = 1 k\Omega$ ;  $C_L = 5 pF$ ;  $E_n = V_{SS}$ ;  $V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ ); 20 log  $\frac{V_{os}}{V_{is}} = -50 dB$ ; see Fig. 7.

- 7.  $R_L = 1 k\Omega$ ;  $C_L = 5 pF$ ;  $E_n = V_{DD}$ ;  $V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ ); 20 log  $\frac{V_{os}}{V_{is}} = -3 dB$ ; see Fig. 7.

Fig. 6.

Fig. 7.

HEF4066B gates

Fig. 8.

Fig. 9.

HEF4066B gates

Fig. 10 Waveforms showing propagation delays from  $V_{is}$  to  $V_{os}$ .

(1)  $V_{is}$  at  $V_{DD}$ ; (2)  $V_{is}$  at  $V_{SS}$ .

Fig. 11 Waveforms showing output disable and enable times.